# A Study of High-Speed Hamming Distance Detection Circuit Utilizing a Neuron CMOS Inverter

Daishi Nishiguchi<sup>1,\*</sup>, Yujiro Harada<sup>2</sup>, Mitsutoshi Yahara<sup>3</sup>, and Kuniaki Fujimoto<sup>4</sup>

<sup>1</sup>Research Institute of Science and Technology, Tokai University, Kanagawa, Japan

<sup>2</sup>Department of Electrical and Electronics Engineering, National Institute of Technology, Kurume College, Fukuoka, Japan

<sup>3</sup> Department of Community and Social Studies, Tokai University, Kumamoto, Japan

<sup>4</sup> Department of Human Information Engineering, Tokai University, Kumamoto-shi, Kumamoto, Japan Email: daishi@tsc.u-tokai.ac.jp (D.N.), y-harada@kurume-nct.ac.jp (Y.H.), yahara@tokai.ac.jp (M.Y.), fujimoto@tokai.ac.jp (K.F.)

Abstract—This study tackles the challenge of optimizing associative memory for efficient data retrieval from large databases, crucial in real-time processing. The authors specifically address the issue of increased detection time in the minimum Hamming distance search associative memory, particularly as the number of data bits grows. This memory system utilizes Hamming distance as a key metric to identify the most similar reference data. Our contribution is the development of a new Hamming distance detection circuit employing neuron Complementary Semiconductor (CMOS) inverters. This proposed circuit significantly outperforms existing models in terms of operational speed. The effectiveness and improved performance of the circuit are validated through simulations using HSPICE, a type of Simulation Program with Integrated Circuit Emphasis (SPICE) demonstrating its potential for more efficient real-time data retrieval applications.

Index Terms—associative memory, hamming distance, high-speed

#### I. INTRODUCTION

Technologies for high-speed retrieval of the most similar data from data stored in a database, such as face recognition, DNA pattern matching, and image compression, are being used in all kinds of situations [1–3]. Recently, with the proliferation of IoT, the amount of information has increased rapidly, and stream data processing, which processes large amounts of data in real-time, has attracted attention. However, when similarity search processing is performed on a computer, data is called up and compared sequentially, so the search time becomes very large as the number of data to be compared increases. Deep learning is currently being actively researched as a method to improve detection and processing time, including in medical and various other

Manuscript received October 10, 2023; revised December 5, 2023; accepted December 29, 2023.

\*Corresponding author

applications [4–6]. However, this method requires a large amount of data and time for training and is not easy to prepare in advance.

To solve these problems, associative memory, one type of functional memory, has been actively studied [7–12]. Associative memory is a memory that, in addition to the usual memory functions, can perform fast search operations by searching the most similar data to the input data in the database in parallel for comparison. Similarity indices include Hamming distance, Manhattan distance, and Euclidean distance [13, 14]. Hamming distance is used for fingerprint recognition and character recognition, while Manhattan distance and Euclidean distance are used for color image recognition, etc.

Humans are good at association and recognition, and given a fragment of information, they can instantly associate what it is from their vast memory. The authors focused on a neuron Complementary Metal Oxide Semiconductor (CMOS) inverter, which has properties similar to those of neurons in the brain [15]. The neuron CMOS inverter has been studied for application to A/D converters and a variety of other circuits since complex operations can be achieved with a simple circuit configuration [16-19]. Therefore, the authors wondered whether this device could be used to realize a high-speed associative memory with a simple configuration. In a minimum Hamming distance search associative memory that retrieves the most similar data using the Hamming distance as an index, the Hamming distance detection circuit that detects the Hamming distance between two data is a very important functional circuit. The authors' research group has proposed a Hamming distance detection circuit by utilizing a neuron CMOS inverter [20-22]. Conventional circuits detect the Hamming distance by converting the Hamming distance into the time it takes for the output signal to change. Therefore, this circuit has the problem that the detection time increases with each increase in the number of data bits.

To solve this problem, this paper proposes a new Hamming distance detection circuit based on neuron CMOS inverters. The proposed circuit can suppress the increase in time with increasing Hamming distance by varying the capacitance between the input terminal and the floating gate of the neuron CMOS inverter. The operation of this circuit was also verified using HSPICE, a circuit simulator.

#### II. CIRCUIT CONFIGURATION

When  $A = (a_1, a_2, ..., a_N)$  and  $B = (b_1, b_2, ..., b_N)$  are *N*-bit binary numbers, the Hamming distance  $D_H$  of *A* and *B* is the sum of different bits and is defined as follows:

$$D_{H} = \sum_{i=1}^{N} \left( a_{i} XORb_{i} \right). \tag{1}$$

where "XOR" is the exclusive OR.

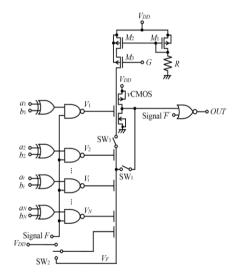

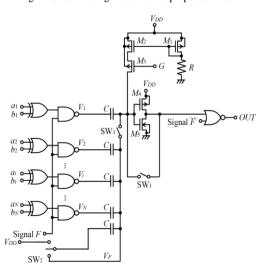

Fig. 1 shows the circuit configuration of the proposed Hamming distance detection circuit using a neuron CMOS inverter. Fig. 2 shows the equivalent circuit of Fig. 1.

Fig. 1. Circuit configuration of the proposed circuit.

Fig. 2. Circuit configuration of the equivalent circuit of the proposed circuit.

In Fig. 1 and Fig. 2,  $V_{DD}$  is the supply voltage,  $A = (a_1, a_2, ..., a_N)$  is the input data,  $B = (b_1, b_2, ..., b_N)$  is the reference data, and F and G are the control signal. The neuron CMOS inverter vCMOS in Fig. 1 is equivalent to the circuit consisting of an inverter with capacitors C and an inverter with transistors  $M_4$  and  $M_5$  in Fig. 2, and the input terminal-to-floating gate capacitance C of the vCMOS is designed to be all equal.

First, the control signal F is set to a low-level, G is set to a high-level, switch  $SW_1$  is turned ON,  $SW_2$  is connected to the lower side, and  $SW_3$  is turned ON. For this operation, the floating gate voltage  $V_F$  of  $\nu$ CMOS is equal to the threshold voltage  $V_{TH}$ , which is expressed by

$$V_F = V_{\rm TH} \tag{2}$$

Since the control signal *F* is a low-level, the outputs of all NANDs become a high-level and the output OUT becomes a low-level.

Next, after SW<sub>1</sub> is turned OFF, SW<sub>2</sub> is connected to the upper side. At this point, the change in the floating gate voltage of  $\nu$ CMOS,  $\Delta V_F$ , when the voltage at one of the input terminals of the CMOS changes to  $\Delta V$  is expressed as follows:

$$\Delta V_F = \frac{C}{C_T} \Delta V \ . \tag{3}$$

where  $C_T$  in the equation is the sum of the capacitance between the input terminal and the floating gate of  $\nu$ CMOS, and is expressed as follows:

$$C_T = (N+1)C. (4)$$

When SW<sub>2</sub> is connected to the upper side, the voltage at the bottom input terminal of the  $\nu$ CMOS in Fig. 1 changes from  $V_{TH}$  to  $V_{DD}$ , and the floating gate voltage  $V_F'$  at this time becomes

$$V_F' = V_{\text{TH}} + \frac{C}{C_T} (V_{\text{DD}} - V_{\text{TH}}).$$

(5)

From this equation,  $V_F'$  exceeds the threshold voltage  $V_{\text{TH}}$ , so the output OUT of  $\nu$ CMOS becomes a low-level.

When the control signal F is set to a high-level, the output  $V_i$  of the NAND changes from a high-level to a low-level if the ith bit  $a_i$  of the input data and the ith bit  $b_i$  of the reference data are not equal. If the Hamming distance between the input data  $A = (a_1, a_2, ..., a_N)$  and the reference data  $B = (b_1, b_2, ..., b_N)$  is  $D_H$ , the output of  $D_H$  NAND changes from the supply voltage  $V_{DD}$  to 0V. When the floating gate voltage  $V_F$  is  $V_F''$  at this time, it is expressed by the following equation.

$$V_F'' = V_{\text{TH}} + \frac{C}{C_T} (V_{\text{DD}} - V_{\text{TH}}) - D_H \frac{C}{C_T} V_{\text{DD}}$$

(6)

From this equation, the floating gate voltage  $V_F''$  is below the threshold voltage  $V_{TH}$ , so the output of vCMOS is at a high-level and the output OUT remains at a low-level.

Finally, SW<sub>3</sub> is turned off, and the control signal G is set to a low-level. With SW<sub>3</sub> turned OFF, the capacitance between the input terminal and the floating gate of the  $\nu$ CMOS is disconnected except for the first input terminal from the top. When the control signal G becomes a low-level, MOS transistor M<sub>3</sub> turns ON and a constant current begins to flow from the current mirror circuit consisting of R,  $M_1$ , and  $M_2$ . This causes the floating gate voltage  $V_F$  to rise linearly from  $V_F''$ . When this exceeds the threshold voltage  $V_{TH}$ , the output of the neuron CMOS inverter becomes a low-level and the output becomes a high-level.

When the constant current flowing through  $M_3$  is I, the time T from when the control signal G is set to a low-level until the output OUT becomes a high-level is expressed by

$$T = \frac{C\left(V_{TH} - V_F''\right)}{I} \,. \tag{7}$$

Substituting (6) into this equation gives

$$T = \frac{C\left\{V_{TH} - V_{TH} - \frac{C}{C_T}(V_{DD} - V_{TH}) + D_H \frac{C}{C_T}V_{DD}\right\}}{I}.$$

(8)

By substituting (4) into this and rearranging the equation, the time T can be expressed as follows:

$$T = D_{H} \frac{C}{I(N+1)} V_{DD} - \frac{C}{I(N+1)} (V_{DD} - V_{TH}).$$

(9)

The time difference  $\Delta T$  when the Hamming distance differs by 1 is expressed by

$$\Delta T = \frac{C}{I(N+1)} V_{DD} \tag{10}$$

From Eq. (9) and (10), it can be seen that the time T from when the control signal G becomes a low-level until the output OUT becomes a high-level is proportional to the Hamming distance. By measuring this time difference, the proposed Hamming distance detection circuit can detect the Hamming distance between two data. Furthermore, it can be seen that although the detection time increases as the Hamming distance  $D_H$  increases, the detection time decreases as the number of data bits in data N increases.

From the above, the proposed circuit reduces the capacitance between the input terminal and the floating gate of the  $\nu$ CMOS by controlling SW<sub>3</sub>, thereby reducing the charging time. Therefore, the proposed circuit does not decrease the detection speed even when the number of data bits N increases and can operate faster than the conventional circuit.

## III. SIMULATION RESULTS

The proposed Hamming distance detection circuit was simulated in HSPICE, HSPICE, a type of Simulation Program with Integrated Circuit Emphasis (SPICE), for the case where the number of bits is 8. The simulations were performed using SPICE parameters for ROHM's

$0.18 \mu$  CMOS process, with a supply voltage of 1.8 V for  $V_{\rm DD}$  and a threshold voltage  $V_{\rm TH}$  for the floating gate of the neuron CMOS inverter designed to be 0.9 V, half of  $V_{\rm DD}$ . The equivalent circuit shown in Fig. 2 was used for the simulation.

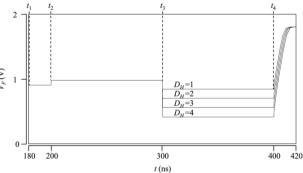

Fig. 3 shows the simulation results of the floating gate voltage of the neuron CMOS inverter when reference data with a Hamming distance of 1-4 is input. In this figure,  $t_1$  represents the point in time when the control signal F is set to a low-level, SW1 is turned ON, SW2 is connected to the lower side, and SW3 is turned ON; t2 represents the point in time when SW<sub>1</sub> is turned OFF and  $SW_2$  is connected to the upper side;  $t_3$  represents the point in time when the control signal F is set to a high-level;  $t_4$ represents the time when SW3 is turned OFF and the control signal G is set to a low-level. The floating gate voltage  $V_F$  is equal to the threshold voltage  $V_{TH}$  at the time  $t_1$  and rises and exceeds  $V_{\text{TH}}$  at  $t_2$ . At the time  $t_3$ , the floating gate voltage  $V_F$  decreases in proportion to the Hamming distance. Finally, at the time  $t_4$ , the floating gate voltage begins to increase linearly. When the floating gate voltage exceeds the threshold voltage of the neuron CMOS inverter, its output changes from a highlevel to a low-level. The simulation results show that the time it takes for the output to change is proportional to the Hamming distance. The proposed circuit can detect the Hamming distance between the two data by this time difference.

Fig. 3. Simulation results of the floating gate voltage.

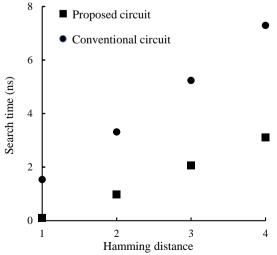

Fig. 4. Relationship between the search time and Hamming distance.

Fig. 4 summarizes the detection times of the proposed circuit and the conventional circuit in [20]. From this figure, it can be seen that the proposed circuit operates faster than the conventional circuit. In the conventional circuit and the proposed circuit, the sum of the capacitances between the input terminals and the floating gate of the neuron CMOS inverter increases with the number of bits. Therefore, in the conventional circuit, the time until the floating gate voltage reaches the threshold voltage after G is set to a low-level increases in proportion to the number of bits. However, the proposed circuit can achieve high-speed operation even as the number of bits increases by disconnecting the capacitance other than the top one during charging.

#### IV. CONCLUSION

In this study, the authors proposed a novel Hamming distance detection circuit using the neuron CMOS inverter. The proposed Hamming distance detection circuit solves the problem of increasing the detection time with increasing the number of bits, which has been a problem in the conventional circuit, by changing the capacitance between the input terminal and the floating gate of the neuron CMOS inverter.

The desired operation of this circuit was confirmed by HSPICE simulation. Furthermore, it was found that the proposed circuit can operate even faster than the conventional circuit.

In future work, it is planned to fabricate a prototype chip of the proposed circuit and conduct experiments and evaluations using the chip.

## CONFLICT OF INTEREST

The authors declare no conflict of interest.

## AUTHOR CONTRIBUTIONS

D. Nishiguchi and Y. Harada conducted the research under the guidance of K. Fujimoto; M. Yahara and K. Fujimoto were responsible for the data analysis; D. Nishiguchi and Y. Harada wrote the paper; all authors reviewed and approved the final version of the paper.

#### **FUNDING**

This work was supported by JSPS KAKENHI Grant Number JP23K03976.

## ACKNOWLEDGMENT

This work was also supported through the activities of VDEC, The University of Tokyo, in collaboration with Cadence Design Systems, NIHON SYNOPSYS G.K., Rohm Corporation, and Toppan Printing Corporation.

## REFERENCES

[1] Y. Kim, M. Imani, N. Moshiri *et al.*, "GenieHD: Efficient DNA pattern matching accelerator using hyperdimensional computing," in *Proc. 2020 Design, Automation & Test in Europe Conference & Exhibition* (DATE), Grenoble, France, 2020, pp. 115–120.

- [2] P. Neamatollahi, M. Hadi and M. Naghibzadeh, "Simple and efficient pattern matching algorithms for biological sequences," *IEEE Access*, vol. 8, pp. 23838–23846, 2020.

- [3] M. Reja, "Empirical evaluation of LZW-compressed multiple pattern matching algorithms," in Proc. 2022 24th International Symposium on Symbolic and Numeric Algorithms for Scientific Computing (SYNASC), Hagenberg / Linz, Austria, 2022, pp. 125– 132.

- [4] C. Li, X. Li, M. Chen and X. Sun, "Deep learning and image recognition," in *Proc. 2023 IEEE 6th International Conference on Electronic Information and Communication Technology* (ICEICT), Qingdao, China, 2023, pp. 557–562.

- [5] A. M. Obaid, A. Turki, H. Bellaaj, and M. Ksontini, "Detection of biliary artesia using sonographic gallbladder images with the help of deep learning approaches," in *Proc. 2022 8th International Conference on Control, Decision and Information Technologies* (CoDIT), Istanbul, Turkey, 2022, pp. 705–711.

- [6] T. Liu, J. Zhang, G. Gao, J. Yang, and A. Marino, "CFAR ship detection in polarimetric synthetic aperture radar images based on whitening filter," *IEEE Trans. on Geoscience and Remote Sensing*, vol. 58, no. 1, pp. 58–81, Jan. 2020.

- [7] K. Pagiamtzis and A. Sheikholeslami, "Content-addressable memory (CAM) circuits and architectures: a tutorial and survey," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 3, pp. 712–727, Mar. 2006.

- [8] P. B. Watta, M. Akkal and M. H. Hassoun, "Decoupled-voting Hamming associative memory networks," in *Proc. International Conference on Neural Networks*, Houston, TX, USA, 1997, pp. 1188–1193.

- [9] A. Annovi, G. Calderini, F. Crescioli et al., "A low-power and high-density associative memory in 28 nm CMOS technology," in Proc. 2017 6th International Conference on Modern Circuits and Systems Technologies (MOCAST), Thessaloniki, Greece, 2017. doi: 10.1109/MOCAST.2017.7937632

- [10] Y. Yano, T. Koide and H. J. Mattausch, "Associative memory with fully parallel nearest-manhattan-distance search for lowpower real-time single-chip applications," in *Proc. Asia and South Pacific Design Automation Conference 2004*, Yokohama, Japan, 2004, pp. 543–544.

- [11] M. A. Abedin, T. Koide and H. J. Mattausch, "Nearest Euclidean distance search associative memory for high-speed pattern matching," *DUET Journal*, vol. 1, no. 2, pp. 31–34, 2011.

- [12] E. Garzón, R. Golman, Z. Jahshan et al., "Hamming distance tolerant content-addressable memory (HD-CAM) for DNA classification," *IEEE Access*, vol. 10, pp. 28080–28093, 2022.

- [13] X. S. Hu, M. Niemier, A. Kazemi et al., "In-memory computing with associative memories: A cross-layer perspective," in *Proc.* 2021 IEEE International Electron Devices Meeting (IEDM), 2021. doi: 10.1109/IEDM19574.2021.9720562

- [14] L. Liu, A. F. Laguna, R. Rajaei et al., "A reconfigurable FeFET content addressable memory for multi-state hamming distance," *IEEE Trans. on Circuits and Systems I: Regular Papers*, vol. 70, no. 6, pp. 2356–2369, 2023.

- [15] T. Shibata and T. Ohmi, "A functional MOS transistor featuring gate-level weighted sum and threshold operations," *IEEE Trans.* on Electron Devices, vol. 39, no. 6, pp. 1444–1455, Jun. 1992.

- [16] R. Ohtsuka, H. Yagi, M. Fukuhara and K. Fujimoto, "Analysis by FPD for neuron CMOS variable logic circuit with FG calibration," *ICIC Express Letters*, vol. 14, no. 10, pp. 985–992, 2020.

- [17] Y. Harada, M. Yahara, K. Eguchi and K. Fujimoto, "A flash type A/D converter using neuron CMOS inverters with threshold compensation circuits," *ICIC Express Letters*, vol. 14, no. 3, pp. 251–256, 2020.

- [18] D. Nishiguchi, M. Fukuhara, M. Yahara and K. Fujimoto, "An electronic neuron using interconnect capacitance and applied to a variable logic circuit," *IEICE Trans. Electron*, vol. 16, no. 7, pp. 741–748, 2022.

- [19] D. Nishiguchi, M. Fukuhara, M. Yahara and K. Fujimoto, "Hamming distance search circuit using interconnect capacitance," *ICIC Express Letters*, vol. 17, no. 6, pp. 659–665, 2022.

- [20] Y. Harada, K. Fujimoto, M. Fukuhara and M. Yoshida, "A minimum hamming distance search associative memory using neuron CMOS inverters," *IEEJ Trans. on Electronics, Information* and Systems, vol. 92, no. 1, pp. 36–42, 2016.

- [21] N. Onji, T. Kurano, T. Saho et al., "A reduction of current consumption of a Hamming distance detector by improvement of

current mirror circuit," in *Proc. 2019 International Symposium on Intelligent Signal Processing and Communication Systems*, Taipei, Taiwan, 2019. doi: 10.1109/ISPACS48206.2019.8986268

[22] T. Saho, Y. Harada, M. Fukuhara, and K. Fujimoto, "Multiple output of similarity data by recalling type associative memory using neuron CMOS inverter," *ICIC Express Letters, Part B, Applications: An International Journal of Research and Surveys*, vol. 11, no. 11, pp. 1095–1104, 2020.

Copyright © 2024 by the authors. This is an open access article distributed under the Creative Commons Attribution License ( $\underline{CC}$  BY- $\underline{NC}$ -ND 4.0), which permits use, distribution and reproduction in any medium, provided that the article is properly cited, the use is non-commercial and no modifications or adaptations are made.

loops (PLLs).

**Daishi Nishiguchi** graduated from Tokai University in 2021 with a bachelor's degree and completed his master's degree at the same university in 2023. In the same year, he began his doctoral studies at Tokai University's graduate school. Concurrently, he was appointed as a specified research assistant at Tokai University, a position he currently holds. His research focuses on neuron electronic circuits and phase-locked

**Yujiro Harada** obtained his Ph.D. in Engineering from Tokai University in 2017. He is currently a full-time assistant professor at the National Institute of Technology, Kurume College, Japan. His main research interests include the A/D converter and the associative memory.

Mitsutoshi Yahara graduated from Kyushu Tokai University (Dept. of Eng.) in 1991, where he completed a master's course in 1993. He was employed as an assistant by Tokai University Fukuoka Junior College where he was a lecturer in 1997, was a professor in 2009, and has been a professor at Tokai University since 2018. He obtained his Ph.D. in Engineering from Tokai University in 2007. His research interests include switched capacitor circuits and phase-locked loops.

Kuniaki Fujimoto graduated from Tokai University (Dept. of Eng.) in 1987, where he completed a master's course in 1989, and was employed as an assistant by Nagasaki Women's Junior College. He was an assistant at Kyushu Tokai University in 1991 and has been a professor at Tokai University since 2010. He obtained his Ph.D. in Engineering from Tokai University in 2009. His research interests include pulsed circuits and digital circuits.